【加法笔记系列】逻辑电路的实现

了解完二极管和 PN 结原理后,就可以看懂简单的逻辑电路了

- 载流子

- 场效应管

- 与门 AND

- 二极管实现

- 继电器实现

- CMOS 实现

- NMOS 实现

- 或门 OR

- 或非 NOR

- 与非 NAND

载流子

在物理学中,载流子(charge carrier)简称载子(carrier),指可以自由移动的带有电荷的物质微粒,如电子和离子。在半导体物理学中,电子流失导致共价键上留下的空位(空穴)被视为载流子。

— Wiki

在半导体中,电子和空穴作为载流子。数目较多的载流子称为多数载流子;在N型半导体中多数载流子是电子,而在P型半导体中多数载流子是空穴。数目较少的载流子称为少数载流子;在N型半导体中少数载流子是空穴,而在P型半导体中少数载流子是电子。[1]

— Wiki

场效应管

场效应管(英语:field-effect **transistor,缩写:FET)是一种通过电场效应控制电流的电子元件。

它依靠电场去控制导电沟道形状,因此能控制半导体材料中某种类型载流子的沟道的导电性。

— Wiki

G 栅极通过控制电压,控制 P 沟道的载流子,从而控制 PN 结的宽度,参考:场效应管及其放大电路

在 Vgs 为 0 时,PN 结最小,导电 N 沟道最宽,导电性能最好

当 Vgs 负电压增大,电子流入 P 沟道,P 沟道载流子减少,N 沟道为平衡 PN 结的内电场,N 沟道的载流子也变小,从而导致 PN 结变宽。

Vds 的原理大致与 Vgs 相同

当 Vds 增强时,也会出现沟道夹断的情况。

此处还待进一步思考

与门

二极管电路实现

vcc:电路供电电压 为10v,假设 3v 以上为高电平,3v 以下为低电平。参考:二极管与门电路原理

| ua | ub | uy |

|---|---|---|

| 0(正偏)/ 0 | 0(正偏)/ 0 | 0.7v / 0 |

| 3v (反偏)/ 1 | 0 (正偏)/ 0 | 0.7v / 0 |

| 0 (正偏)/ 0 | 3v (反偏)/ 1 | 0.7v / 0 |

| 3v (正偏)/ 1 | 3v (正偏)/ 1 | 3.7v / 1 |

继电器实现

- 仅 A、B 都为高电平,使继电器将开关闭合,从而使得 Y 导通为高电平。

CMOS与门

PN结指向内的为NMOS管, PN 结指向外部的为 PMOS [4]

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。 PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。[5]

T1, T2, T5 为 PMOS,0 导通,1 不导通

T3,T4,T6 为 NMOS,1 导通,0 不导通

| A,B | T1,T2,T3,T4 | T5,T6 栅极 | T5,T6 | Y |

|---|---|---|---|---|

| 0,0 | 通,通,不通,不通 | 1 | 不通,通 | 0 |

| 1,0 | 不通,通,通,不通 | 1 | 不通,通 | 0 |

| 0,1 | 通,不通,不通,通 | 1 | 不通,通 | 0 |

| 1,1 | 不通,不通,通,通 | 0 | 通,不通 | 1 |

NMOS 与门

假设与 a 直连的 NMOS 为 T1,与 b 直连的 NMOS 为 T2,与 F 直连的为 T3

- 仅 a、b 都为 1 时,T3 栅极为低电平,从而 T3 不导通,导致 F 为高电平

- 其余情况,任意 a、b 为 0 时,与 T3 栅极为高电平并导通,使得 F 接地,为低电平。

或门

| A | B | L |

|---|---|---|

| 0(正偏)/ 0 | 0(正偏)/ 0 | 0v / 0 |

| 5v (正偏)/ 1 | 0 (反偏)/ 0 | 5v / 1 |

| 0 (反偏)/ 0 | 5v (正偏)/ 1 | 5v / 1 |

| 5v (正偏)/ 1 | 5v (正偏)/ 1 | 5v / 1 |

非门

- a 高电平时,F 接地为低电平,反之成立

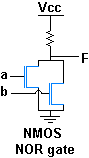

或非 NOR

或非门具有函数完备性,和与非门一样可以仅用其实现其他所有的逻辑功能。

电路图如下,并假设与 a 直连的 MOS 为 T1,与 b 直连的 MOS 为 T2

当 a、b 中任意一个为高电平,则 F 和 GND 连接为低电平,只有 a、b 都为低电平时,F 才为高电平。

| 输入A | B | 输出A NOR B |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

与非 NAND

| NMOS | CMOS |

|---|---|

NMOS, 仅 A,B 都为高电平使得 T2,T3 导通,Y 才为低电平

CMOS 如下:

| A,B | T1,T2,T3,T4 | Y |

|---|---|---|

| 0,0 | 通,通,不通,不通 | 1 |

| 0,1 | 通,不通,不通,通 | 1 |

| 1,0 | 不通,通,通,不通 | 1 |

| 1,1 | 不通,不通,通,通 | 0 |

Comments

Leave a comment